Application-Specific Integrated Circuit Design

At the Integrated Information Processing (IIP) Group, we strive to develop application specific integrated circuits (ASICs) that achieve highest throughput, lowest power, minimal latency, and best solution quality. In order to accomplish this task, we develop new and transformative algorithms from the ground up, which are designed to be hardware friendly. While implementing our algorithms in hardware, we regularly discover new theoretical aspects and architecture-level tricks that that further improve efficiency. We also levarage emerging architecture and ASIC-design concepts, including in- and near-memory processing, and semi-custom standard-cell design.

Our unique cross-stack design approach that jointly considers theory, algorithms, and hardware design, allows us to develop state-of-the-art ASICs for a number of different applications.

Our ASIC designs are often done in collaboration with the Microelectronics Design Center. Some of our recent ASIC implementations are as follows:

Sandman (2023; GF 22FDX)

This 5mm2 chip is the first multiuser MIMO receiver ASIC that mitigates jamming attacks. Sandman implements the algorithm of the same name, which was also developed by the IIP Group. It performs joint jammer mitigation (via spatial filtering) and data detection (using a box prior on the data symbols). The design supports 8 user equipments (UEs) and 32 basestation (BS) antennas, QPSK and 16-QAM with soft-outputs, and enables the mitigation of single-antenna barrage jammers and smart jammers. The fabricated 22 nm FD-SOI ASIC includes preprocessing, has a core area of 3.78 mm2, achieves a throughput of 267 Mb/s while consuming 583 mW, and is the only existing design that enables reliable data detection under jamming attacks. A preprint is available on external page arXiv.

Kraken (2021; GF 22FDX)

This 9mm2 chip contains several designs based on the Parallel Ultra-Low Power (PULP) architecture, developed by the Digital Circuits and Systems Group. One of those designs is PULPO, which was created by the IIP group. PULPO is the first floating-point baseband-processing accelerator for massive MIMO basestations, and is designed to accelerate three atomic operations that are critical to several linear and nonlinear algorithms for both uplink and downlink. To increase its programmability and flexibility, PULPO is integrated in a system-on-chip (SoC) with a tight coupling to the system's data memory, facilitating data exchange and co-operation with 8 PULP RISC-V cores. A preprint is avilable on the ETH Research Collection.

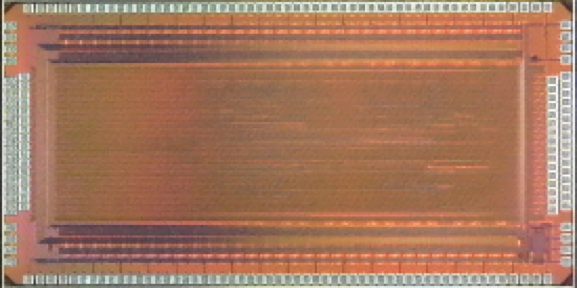

SIR PPAC (2020; TSMC 65nm)

This 4mm x 2mm mixed-signal chip constitutes the first scalable all-digital massive MU-MIMO spatial equalizer. The ASIC is designed for a 32-antenna base station serving up to 16 user terminals. The design contains an analog front end composed by 64 programmable-resolution SAR ADCs, which were designed by our collaborators from the external page Molnar Research Group at Cornell University. Furthermore, the chip implements novel low-resolution techniques for energy-efficient channel estimation, equalization, and beamspace processing. In specific, the ASIC features our patented beamspace channel estimation (BEACHES) algorithm, our high-throughput streaming-multiplierless (SMUL) FFT, and our all-digital, processing-in-memory (PIM) accelerator PPAC, which is implementing low-resolution finite-alphabet MMSE (FAME) equalization.

SIR PPAC was awarded with the Best Paper Award at ESSCIRC 2021. A preprint is available on external page arXiv.

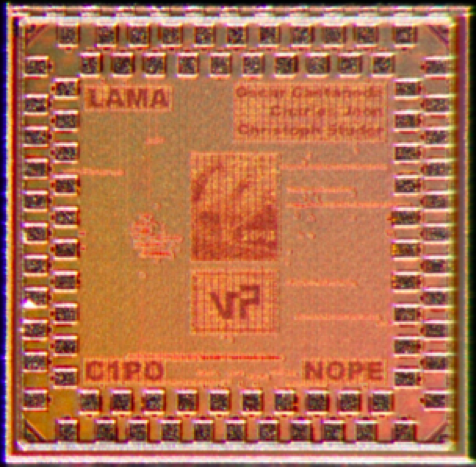

LAMA, C1PO, and NOPE (2018; TSMC 28nm)

This 2mm2 chip contains three different accelerators for large multi-antenna wireless communication systems. In specific, the ASIC includes (i) the large-MIMO approximate message passing (LAMA) data detector, which offers near-optimal performance for realistic massive multiuser MIMO wirelss, (ii) the biconvex 1-bit precoding (C1PO) algorithm, which is the first ASIC implementation of a 1-bit precoder for the massive multiuser MIMO downlink, and (iii) the non-parametric equalizer (NOPE), a matrix-inversion-free, parameter-free equalizer that is robust to hardware impairments. All three designs exploit near-memory processing and energy-efficient latch-arrays to tightly integrate memory and computations. The ASIC also features the artwork of three lamas contemplating the horizon, symbolizing the three implemented designs. A preprint is available on external page arXiv.