Paper on a Matrix Preprocessing ASIC for Massive MIMO accepted at ESSERC 2024

A preprint is available on arXiv!

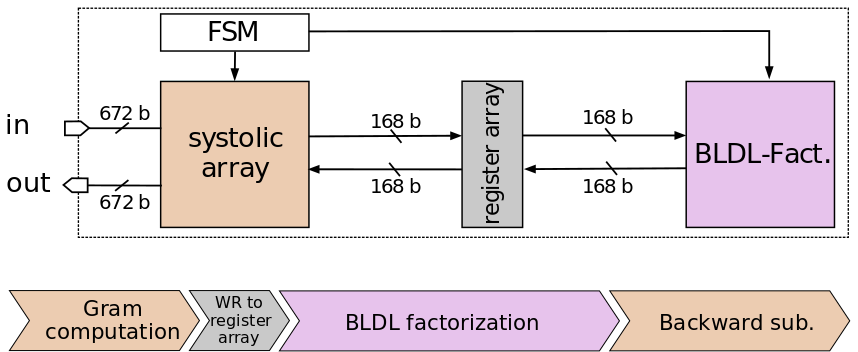

Massive multiuser (MU) multiple-input multiple-output (MIMO) enables concurrent transmission of multiple users to a multi-antenna basestation (BS). To detect the users' data using linear equalization, the BS must perform preprocessing, which requires the inversion of a matrix whose dimension equals the number of user data streams. Explicit inversion of large matrices is notoriously difficult to implement due to high complexity, stringent data dependencies that lead to high latency, and high numerical precision requirements. We propose a novel preprocessing architecture based on the block-LDL matrix factorization, which improves parallelism and, hence, reduces latency. We demonstrate the effectiveness of our architecture using measurements of a 22FDX ASIC, which is the first fabricated preprocessing engine for massive MU-MIMO with 64 BS antennas and 16 single-antenna users.

The paper "A 1.2 mm2 416 mW 1.44 M mat/s 64x16 Matrix Preprocessing ASIC for Massive MIMO in 22FDX" is co-authored by Darja Nonaca and Prof. Christoph Studer and will be presented at the European Solid-State Electronics Research Conference (ESSERC) in Bruges in September 2024. A preprint is available on external page arXiv.

Note that the preprocessing engine was implemented on the Mothra ASIC, which is shared with a data detector for mmWave systems designed by Zixiao Li.